Nhu cầu về bộ nhớ lưu trữ hay bộ nhớ không bay hơi (NVM – non-volatile memory) nhúng trong các hệ thống trong chip (SoC – System on Chip) đang tăng trưởng theo cấp số nhân trong những năm gần đây do sự phát triển của các ứng dụng mới trong lĩnh vực truyền thông và các thiết bị điện tử dân dụng. Hơn nữa, dung lượng lưu trữ của bộ nhớ trong chip SoC đang ngày càng gia tăng để đáp ứng các yêu cầu ngày càng phức tạp của phầm mềm ứng dụng cũng như trình điều khiển. Do có lợi thế về số lần ghi xóa (lên đến hàng triệu lần so với hàng trăm ngàn lần của EEPROM – người dịch), bộ nhớ Flash tích hợp (eFlash – embedded Flash) thường được sử dụng nhằm lưu trữ dữ liệu và mã điều khiển quan trọng trong các chip hiện nay. Ngoài ra, eFlash cho phép lập trình sau khi đã triển khai (field programming). Đặc tính này tạo sự linh động tuyệt vời giúp bộ lưu trữ eFlash có thể đáp ứng được cả các thay đổi lớn ở mức hệ thống vào phút cuối.

Công nghệ eFlash thường được phát triển theo sau công nghệ nền (là công nghệ nhúng eFlash) khoảng ba năm và chủ yếu hướng đến các ứng dụng thuộc đợt thứ hai; do đó, ngoài vấn đề độ tin cậy, một công nghệ bộ nhớ nhúng (dùng lưu trữ – người dịch) cần có các đặc tính sau:

- Dễ dàng tích hợp vào công nghệ nền (Logic baseline process) hiện có với số mặt nạ gia tăng không đáng kể nhằm đảm bảo chi phí chế tạo thấp

- Không làm thay đổi mô hình và đặc tính silicon của công nghệ nền, điều này cũng có nghĩa là các IP (Intellectual Property – thành quả hoặc tài sản trí tuệ) cũ vẫn được bảo đảm hoạt động

- Tương thích với transistor hiện có

- Hiệu suất chế tạo (yield) cao và dễ dàng kiểm tra thử nghiệm

- Cho phép tích hợp bộ lưu trữ dạng Flash và EEPROM trên cùng một chip

Công nghệ bộ nhớ Silicon-Oxide-Nitride-Oxide-Silicon (SONOS) có đầy đủ các đặc tính kể trên, và do vậy rất phù hợp cho bộ nhớ Flash tích hợp.

SONOS hay Công Nghệ Bộ Nhớ Bẫy Điện Tích

Một bộ nhớ SONOS sử dụng một lớp cách điện, thường là silicon nitride, có các bẫy điện tích để làm lớp lưu điện tích. Những bẫy điện tích này sẽ thu các hạt điện tích trong kênh dẫn của MOS transistor và lưu giữ chúng tại đó. Bộ nhớ dạng này còn được gọi là bộ nhớ bẫy điện tích. Do lớp lưu điện tích này là lớp cách điện, nên cơ chế lưu trữ này ít bị ảnh hưởng bởi khuyết tật lỗ kim (pinhole defects – là tình trạng lớp cách điện bị khuyết tật dạng lỗ nhỏ hoặc vệt nhỏ trên bề mặt. Điều này có thể ảnh hưởng lên cơ chế ghi/xóa của các cổng thả nổi – người dịch), và nó còn có ưu điểm về mặt hiệu suất chế tạo và khả năng lưu trữ dữ liệu.

Do các bộ nhớ dạng SONOS có rất ít các bit “yếu”, nên việc kiểm tra trở nên dễ dàng. Một ưu điểm chính nữa của công nghệ SONOS là yêu cầu mức điện áp cho việc ghi hoặc xóa thấp hơn so với công nghệ cổng thả nổi (floating gate). Công nghệ SONOS ở 65nm thực hiện việc ghi và xóa dựa trên cơ chế truyền tĩnh điện Folwer – Nordheim, nên đã cải thiện đáng kể độ bền lưu trữ của bộ nhớ so với công nghệ sử dụng cơ chế truyền điện tích nóng (hot electron injection – HEI).

Ngoài ra, với công nghệ nền 65nm CMOS hiện có, việc tích hợp thêm transistor SONOS chỉ cần thêm ba lớp mặt nạ. Hơn nữa, nhiệt lượng toả ra từ các transistor SONOS này không lớn, nên ít ảnh hưởng tới đặc tính điện của các CMOS FET hiện có. Thêm vào đó, các transistor SONOS có chung các bước xử lý chính trong chế tạo với transistor CMOS. Do đó, các cực của transistor SONOS như nguồn (source), máng (drain) và cổng (gate) giống hoàn toàn như transistor CMOS. Điều này giúp cho toàn bộ quá trình xử lý chế tạo công nghệ SONOS tích hợp trở nên đơn giản. Hơn nữa, công nghệ SONOS ở 65nm sử dụng điện áp cho ghi và xóa thấp, nên mạch nhớ Flash có thể sử dụng các lớp oxit vốn đang được dùng cho các mạch logic hoặc cho các mạch giao tiếp vào/ra (IO) mà không cần đến các lớp oxit dùng cho điện áp cao (độ dày lớp oxit phải dày hơn – người dịch).

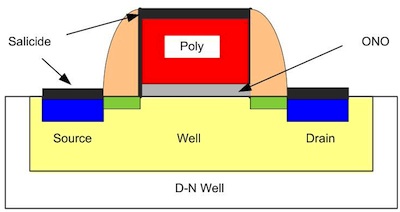

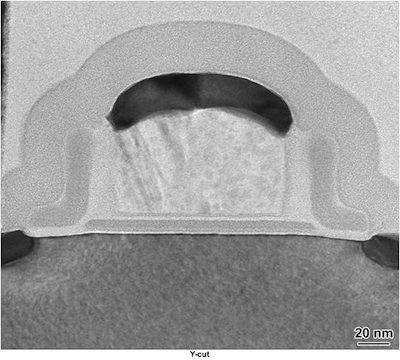

Mô hình mặt cắt ngang của SONOS FET được mô tả trong hình 1, và mặt cắt ngang nhìn dưới kính hiển vi TEM của một transistor SONOS thực tế tích hợp trong công nghệ nền CMOS 65nm được mô tả trong hình 2. Đây là một transistor SONOS được chế tạo bởi quy trình CMOS điển hình. Các cực của transistor (cực nguồn, cực máng và cực cổng) đã xử lý qua quá trình salicide. Cực cổng được tạo thành từ salicided polysilicon. Thông thường, công nghệ SONOS tích hợp có nhiều tùy chọn khác nhau cho tế bào nhớ như tốc độ ghi từ 1 – 5ms, và tốc độ xóa từ 5 – 10ms tùy theo ứng dụng và kiến trúc hệ thống mà không ảnh hưởng đến độ tin cậy của bộ nhớ. Cấu trúc của tế bào này có thể sử dụng cho Flash hoặc EEPROM.

Độ tin cậy của tế bào nhớ SONOS

Một yêu cầu chính yếu của bộ nhớ không bay hơi là độ tin cậy. Đặc tính điện áp ngưỡng trong suốt vòng đời của một tế bào NVM có thể bị suy giảm bởi số lần (chu kỳ) ghi và xóa (endurance, còn gọi là độ bền của NVM – người dịch), hoặc bởi thời gian lưu trữ dữ liệu (data retention).

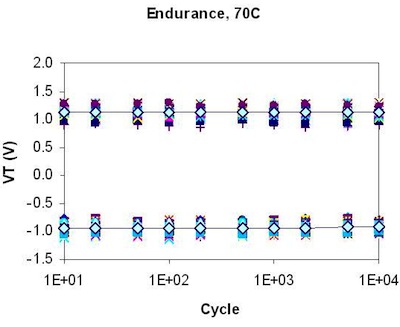

Thông thường, độ bền (endurance) của tế bào nhớ SONOS được xác định bằng cách cho tế bào thực hiện liên tiếp một số lượng cụ thể các chu kỳ ghi và xóa, và đồng thời đo mức thay đổi của các điện áp ngưỡng (Vt) tại trạng thái ghi và trạng thái xóa. (Quá trình ghi và xóa này sẽ ảnh hưởng đến điện áp ngưỡng của mỗi tế bào nhớ, cụ thể là làm suy giảm sai biệt điện áp ngưỡng giữa trạng thái ghi và trạng thái xóa. Mỗi tế báo nhớ ở trạng thái ghi sẽ có mức điện áp ngưỡng cụ thể thường là dương, còn tế bào nhớ ở trạng thái xóa sẽ có mức điện áp ngưỡng là âm – người dịch).

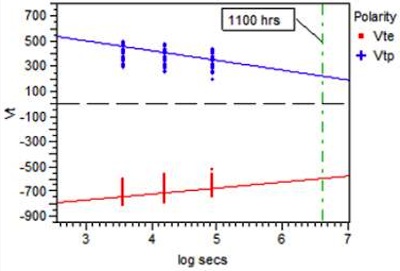

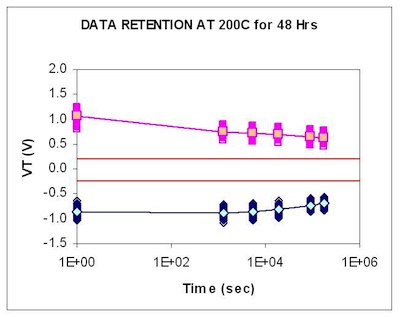

Khả năng lưu (retention) dữ liệu được xác định bằng cách cho một tế bào nhớ SONOS đã được thực hiện một số lượng cụ thể chu kỳ ghi và xóa, và sau đó đo mức thay đổi của các điện áp ngưỡng (Vt) theo thời gian cho trạng thái ghi và trạng thái xóa ở nhiệt độ rất cao. (Tại nhiệt độ cao thì điện tích sẽ hoạt động mạnh, dẫn đến dễ có sự thay đổi tính tích điện tại các “bẫy điện tích”, làm cho có sự thay đổi điện áp ngưỡng. Sai biệt điện áp ngưỡng giữa trạng thái xóa và ghi có xu hướng giảm. Khi sự sai biệt này nhỏ đến mức nào đó thì giá trị được lưu trữ của bộ nhớ có thể bị “nghi ngờ” và sẽ không còn được sử dụng. Hình 4 mô tả khá rõ vấn đề này – người dịch). Hình 3 và hình 4 mô tả đặc tính điện áp ngưỡng của bộ nhớ theo số chu kỳ ghi/xóa và theo thời gian lưu trữ dữ liệu của NVM.

Sự thay đổi của đặc tính điện áp ngưỡng theo số lần chu kỳ ghi xóa là không đáng kể sau 10 ngàn lần ở 700 độ C (Hình 3). Còn đặc tính điện áp ngưỡng theo thời gian cho thấy sai biệt điện áp ngưỡng ở cuối vòng đời (End-of-Life Vt) vẫn lớn hơn nhiều so với sai biệt điện áp ngưỡng tối thiểu để nhận ra trạng thái của tế bào nhớ như Hình 4. (Theo thời gian, điện áp ngưỡng của trạng thái ghi (dương) có xu hướng giảm, và điện áp ngưỡng của trạng thái xóa (âm) có xu hướng tăng lên. Khi sai biệt điện áp ngưỡng (giữa trạng thái ghi và xóa) suy giảm đến các mức tối thiểu (minimum window), thì mạch đọc sẽ khó nhận biết được tế bào nhớ đang ở trạng thái ghi hay trạng thái xóa – người dịch).

Tích hợp SONOS vào quy trình chế tạo 65nm

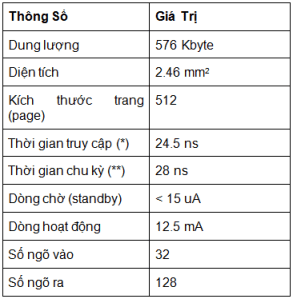

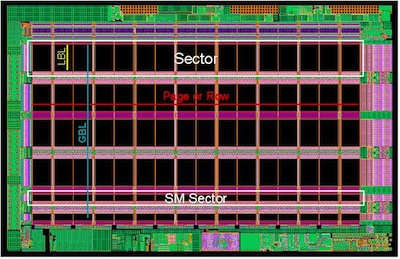

Trong quy trình tích hợp cho việc chế tạo, ngoài việc tích hợp thêm công nghệ SONOS, thì còn bao gồm cả việc tạo ra các cực cổng đôi (dual gate) để chip có khả năng tương thích với nhiều mức điện áp nguồn cung cấp khác nhau. Gần đây, Cypress đã tích hợp thành công SONOS vào trong công nghệ nền LL65 (Low Leakage 65nm) của UMC, thông qua chip thử nghiệm bộ nhớ dạng flash có dung lượng 576kB (Hình 5). Các đặc tính chính của chip này được mô tả trong Bảng 1. Bộ nhớ flash này vẫn thể hiện khả năng lưu trữ tốt ở 1500C, sau 10 nghìn chu kỳ ghi xóa (Hình 6).

Bảng 1: Đặc tính chip nhớ SONOS trên công nghệ LL65 UMC

Giải thích thêm của người dịch:

(*): Thời gian truy cập: là khoảng thời gian tối thiểu giữa lệnh đọc và ghi/xóa.

(**): Thời gian chu kỳ: là khoảng thời gian tối thiểu giữa hai thời gian truy cập liên tiếp

Hình 6: Đặc tính lưu trữ của chip thực nghiệm (Vte: Điện áp ngưỡng của trạng thái xóa. Vtp: Điện áp ngưỡng của trạng thái ghi)

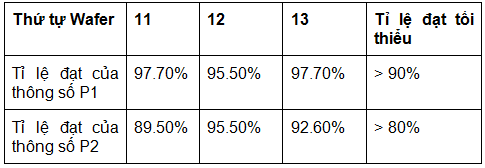

Mức tỏa nhiệt thấp của SONOS khi được tích hợp sẽ không ảnh hưởng đáng kể đến hoạt động của các linh kiện CMOS hiện có. Điều này có nghĩa là chỉ cần vài thay đổi nhỏ, tất cả các IP trên nền công nghệ CMOS hiện tại có thể được tái sử dụng trên nền công nghệ mới. Quá trình tích hợp SONOS chưa cho thấy ảnh hưởng đáng kể nào lên hoạt động của các lõi IP, cũng như tính đồng nhất của các linh kiện trong quá trình sản suất quy mô lớn trên công nghệ nền 65nm. Hơn nữa, hiện tại còn cho thấy quá trình tích hợp này cũng không ảnh hưởng đến hiệu suất chế tạo của công nghệ hiện có.

Bảng 2 cho thấy tính đồng nhất của các linh kiện thông qua các thông số chính của transistor trên công nghệ đã tích hợp SONOS và trên công nghệ nền. P1 là thông số ưu tiên số một, P2 là thông số ưu tiên số hai.

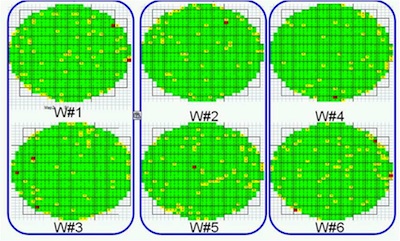

Các sơ đồ phân bố xác suất chế tạo thành công của wafer (Yield wafer maps) cho chip SRAM có tích hợp công nghệ SONOS được so sánh với sơ đồ tương ứng công nghệ nền được mô tả trong Hình 7. Kết quả trong hình này cho thấy tác động không đáng kể của việc tích hợp SONOS lên công nghệ nền.

Ngoài ra, chỉ với vài thay đổi nhỏ về điều kiện ghi và xóa, tế bào SONOS này có thể được sử dụng để xây dựng bộ nhớ EEPROM. Do vậy, việc tích hợp Flash và EEPROM trên một chip sẽ trở nên đơn giản với công nghệ SONOS.

Kết luận

Công nghệ SONOS là công nghệ có chi phí thấp, độ tin cậy cao, để tích hợp bộ nhớ không bay hơi vào hệ thống logic nền. Các thiết kế trên công nghệ CMOS có sẵn sẽ không bị ảnh hưởng khi tích hợp thêm công nghệ SONOS. Công nghệ này có số lượng chu kỳ ghi xóa và khả năng lưu trữ tốt, và có thể được chuyển sang sử dụng trên các thế hệ công nghệ nền mới hơn mà không cần thay đổi nhiều về quy trình tích hợp. Cypress đã thành công trong việc tích hợp công nghệ SONOS của họ vào trong quy trình chế tạo nền 65nm của UMC, và đã thử nghiệm thành công với một bộ nhớ flash.

Tác giả:

Krishnaswamy Ramkumar, kỹ sư cao cấp:

Krishnaswamy Ramkumar đã tham gia nghiên cứu và phát triển công nghệ bán dẫn cao cấp tại công ty bán dẫn Cypress từ năm 1993. Trong suốt thời gian này, ông đã tham gia phát triển công nghệ bán dẫn từ 0.5um đến 65nm. Công việc của ông chủ yếu tập trung vào các kỹ thuật tiền xử lý (front end processes) như rãnh cách điện nông (Shallow trench Isolation), oxy hóa cực cổng, và tạo hình lớp ONO. (Front end processes: là để chỉ các bước xử lý các lớp (layer) như actives, diffusion, poly, oxide, contact… Trong khi đó, back end processes là để xử lý các lớp từ kim loại và via – người dịch). Ông giữ 55 sáng chế ở Mỹ. Ramkumar lấy bằng thạc sỹ và tiến sỹ từ Viện Khoa học Ấn Độ (Indian Institute of Science – IIS). Trước khi làm việc cho Cypress, ông tham gia giảng dạy tại IIS, và hỗ trợ nghiên cứu tại Viện Bách Khoa Rensselaer (Rensselaer Polytechnic Institute), Troy, New York, Mỹ.

Bo Jin, giám đốc quản lý:

Bo Jin điều hành trực tiếp mảng kinh doanh IP của Cypress, cũng như phát triển quan hệ kinh doanh chiến lược ở khu vực châu Á. Trước đó, Bo Jin làm giám đốc chế tạo của Cypress.

Bo phát triển sự nghiệp của mình trên nhiều lĩnh vực, bao gồm quản lý sản phẩm, quản lý chương trình thiết kế, và các vị trí khác trong nghiên cứu và phát triển công nghệ trong những năm đầu tham gia Cypress. Bo bắt đầu công việc từ vị trí kỹ sư giám sát hoạt động sản suất vào ban đêm. Bo lấy bằng cử nhân ngành Khoa học Vật liệu và cử nhân kinh tế và quản trị kinh doanh tại đại học Giao Thông Thượng Hải (Shanghai Jiao Tong University) vào năm 1992. Ông lấy bằng thạc sỹ về khoa học vật liệu tại Đại học Bang Arizona, và đã hoàn thành thạc sỹ quản trị kinh doanh tại trường kinh doanh Harvard trong năm 2007. Ông giữ 15 chứng nhận sáng chế tại Mỹ.

Bo hiện là chủ tịch Hiệp hội Bán dẫn Trung Quốc tại Bắc Mỹ (North America Chinese Semiconductor Association – NACSA), một tổ chức phi chính phủ làm cầu nối giữa thung lũng Sillicon ở Mỹ và Trung Quốc, với hơn 4000 thành viên.

- Nguyên bản tiếng Anh: “Advantages of SONOS memory for embedded flash technology”, Krishnaswamy Ramkumar and Bo Jin, Cypress Semiconductor, EE Times.com, Septemper 2011.

- Người dịch: Hồ Quang Tây

- Hiệu chỉnh: Tạ Minh Chiến, Phạm Duy Đông

Không hiểu cơ chế đọc của bộ nhớ NVM thế nào nhỉ? Làm sao để mạch phân biệt được trạng thái “0” hay “1” của một bit?

Trong NVM, để phân biệt một cell (tạm gọi là memory cell) trạng thái “0” hoặc “1” thì thường có mạch Sense Amplifier (SA) và reference cell (cell tham chiếu). Trong memory cell nhớ và reference cell có một tín hiệu là Bit Line (BL). Dựa vào đặc tính của BL của memory cell đang ở trạng thái Erase và Program, và dùng SA để so sánh nó với BL của reference cell thì sẽ xác định được memory cell đó đang ở trạng thái “0” hoặc “1”.

Nguyên lý chung là như vậy, tuy nhiên, có một vài kỹ thuật khác có thể không cần dùng reference cell vẫn có thể xác định được trạng thái của memory cell.

Tây.