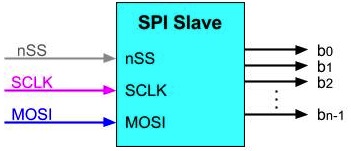

Điều làm cho giao tiếp SPI phổ biến chính là tính đơn giản của nó không chỉ trong trong giao thức mà còn trong cả cách thực hiện bằng mạch điện tử. Trở lại với tình huống dẫn dắt chúng ta đến với việc thiết kế mạch giao tiếp SPI: một lượng bit điều khiển cần phải được chuyển vào bên trong một con chíp tổng hợp tần số để điều khiển hoạt động của nó. Bởi vì con chíp chưa có nhu cầu phải truyền dữ liệu ra bên ngoài theo đường MISO, ta chỉ cần thiết kế mạch SPI Slave với 3 đường tín hiệu: SS, SCLK, và MOSI như trong Hình 8. Các bit dữ liệu được gửi vào trên đường MOSI sẽ được “nhớ” trong mạch SPI và được truy xuất bởi các mạch điện khác thông qua các chân b0, b1, b2, …

Hình 8: Sơ đồ khối thể hiện các tín hiệu vào/ra cho mạch SPI Slave. Đây là mạch SPI Slave đơn giản chỉ có khả năng nhận dữ liệu vào thông qua chân MOSI. Các bit dữ liệu mà SPI Slave nhận được sẽ được truy xuất qua các chân b0, b1, b2, …

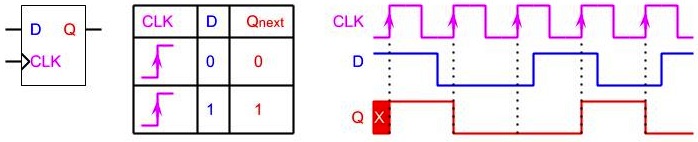

Trước tiên, để lưu trữ các bít dữ liệu gửi vào SPI Slave ta sử dụng các DFF (D flip-flop). Mỗi bit dữ liệu sẽ được lưu bởi một DFF. Ta sẽ nhắc lại một chút về cách hoạt động của DFF ở đây để tiện theo dõi còn chi tiết cách thiết kế DFF có thể được tham khảo trong các sách VLSI (thực ra thì các thư viện standard cell luôn có sẵn mạch DFF nên ta cũng ít khi phải tự thiết kế DFF). Hình 9 mô tả hoạt động của một DFF cạnh lên (rising-edge-triggered DFF) có nghĩa là vào thời điểm tín hiệu CLK (clock) chuyển từ thấp sang cao thì giá trị ở chân D (data) được đưa vào lưu giữ bên trong DFF (và giá trị này cũng đồng thời được hiển thị ở chân Q). Ta nói một DFF có khả năng lưu giữ một bít dữ liệu là vì tín hiệu ở chân Q của DFF sẽ được duy trì nếu DFF được cấp nguồn liên tục và ta không cố ý thay đổi giá trị của DFF bằng cách thay đổi mức điện áp ở chân D và thiết lập một cạnh lên ở chân CLK.

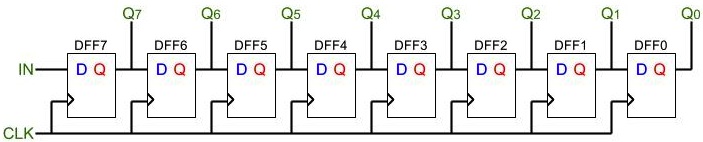

Trở lại với bài toán thiết kế SPI Slave, để đơn giản, hãy giả sử ta muốn gửi mỗi lần 8 bit (n=8) vào con chíp thông qua mạch SPI Slave. Ta sẽ dùng 8 DFF để lưu trữ 8-bit này. 8 DFF được kết nối với nhau thành một chuỗi như trong Hình 10. Đây chính là một thanh ghi dịch (shift-register) có độ rộng 8 bit và hoạt động như một bộ nhớ đệm (input buffer) ở ngõ vào MOSI của mạch SPI Slave. (Nếu muốn gửi nhiều bit hơn trong một lần thực hiện giao tiếp, ta chỉ việc mở rộng bộ nhớ đệm này lên một cách tương ứng). Giá trị được lưu trữ trong bộ nhớ đệm này là Q0Q1Q2Q3Q4Q5Q6Q7. Dữ liệu được đưa vào bộ nhớ đệm qua chân IN. Khi tín hiệu CLK có một cạnh lên thì:

- DFF0 chuyển giá trị của Q1 (chân D) sang Q0 (chân Q)

- DFF1 chuyển giá trị của Q2 (chân D) sang Q1 (chân Q)

- DFF2 chuyển giá trị của Q3 (chân D) sang Q2 (chân Q)

- DFF3 chuyển giá trị của Q4 (chân D) sang Q3 (chân Q)

- DFF4 chuyển giá trị của Q5 (chân D) sang Q4 (chân Q)

- DFF5 chuyển giá trị của Q6 (chân D) sang Q5 (chân Q)

- DFF6 chuyển giá trị của Q7 (chân D) sang Q6 (chân Q)

- DFF7 chuyển giá trị của IN (chân D) sang Q7 (chân Q)

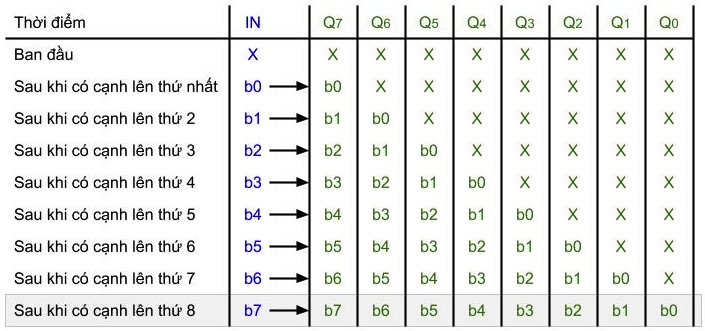

Như vậy các DFF đã dịch các bit dữ liệu được lưu trữ sang phải một vị trí và nhận thêm một bit dữ liệu mới từ chân IN vào Q7. Các xung CLK nối tiếp nhau sẽ làm cho bit dữ liệu ở chân IN được dịch chuyển lần lượt vào bên trong bộ nhớ đệm. Sau 8 xung CLK thì bit dữ liệu được truyền vào đầu tiên sẽ được lưu ở Q0 còn bit dữ liệu được truyền vào cuối cùng được lưu ở Q7. Chi tiết về hoạt động của thanh ghi dịch được minh hoạ trong Bảng 1.

Hình 10: Bộ nhớ đệm nối với chân MOSI là một thanh ghi dịch (shift-register) được tạo thành từ các DFF để lưu trữ các bit được truyền vào.

Bảng 1: Giá trị các bit được lưu trong bộ nhớ đệm ở các thời điểm khác nhau. Sau xung clock thứ 8, 8 bit dữ liệu đã được truyền vào bên trong bộ nhớ đệm và có thể được đọc ra ở các chân từ Q0 đến Q7.

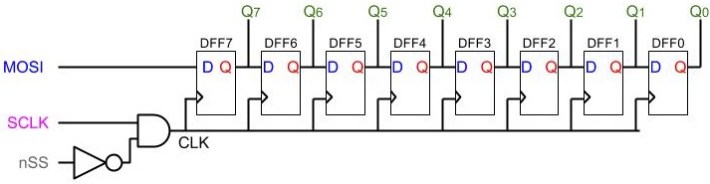

Ta có thể thấy bộ nhớ đệm tạo thành bởi thanh ghi dịch có thể sample được tín hiệu dữ liệu trên đường MOSI nếu chân IN được nối với MOSI và chân CLK được nối với SCLK. Để biến thanh ghi dịch thành mạch SPI Slave ta cần bổ sung thêm đường tín hiệu Slave Select. Điều này có thể thực hiện bằng cách thêm các cổng logic để chỉ cho phép tín hiệu SCLK đi qua khi tín hiệu Slave Select được kích hoạt. Hình 11 trình bày cách dùng một inverter và một cổng AND để kết hợp tín hiệu SCLK và nSS và tạo thành tín hiệu CLK cho các DFF của bộ nhớ đệm.

Hình 11: Mạch SPI Slave hoạt động ở Mode 0 hoặc Mode 3 và có khả năng nhận 8 bit dữ liệu trong mỗi lần truyền.

Mạch trong Hình 11 cũng chính là mạch SPI Slave mà ta cần. Do tín hiệu MOSI được sample bởi DFF7 ở cạnh lên của SCLK, mạch SPI Slave này hoạt động ở Mode 0 hoặc Mode 3.

…

(xem tiếp Phần 4: Kết hợp SPI với thanh ghi + Phần cuối: SPI Master)

- Phần 1: Giới thiệu

- Phần 2: Nguyên lý hoạt động

- Phần 3: Thiết kế mạch SPI Slave

- Phần 4: Kết hợp SPI với thanh ghi + Phần cuối: SPI Master

Pingback: SPI cho dân analog – Phần 2/4: Nguyên lý hoạt động | Chuyên Mục Công Nghệ

Pingback: SPI cho dân analog – Phần 1/4: Giới thiệu | Chuyên Mục Công Nghệ

Pingback: SPI cho dân analog – Phần 4/4: Kết hợp SPI với thanh ghi – Phần cuối: SPI Master | Chuyên Mục Công Nghệ