…

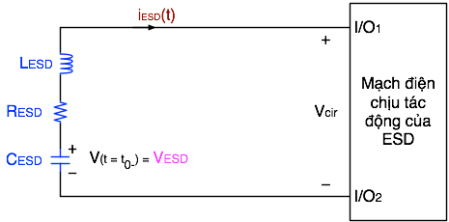

Hình 1: Mạch điện tương đương của quá trình phóng điện do tĩnh điện theo các mô hình HBM, MM, và CDM.

Trong mô hình tương đương ở Hình 1, dòng điện chạy trong mạch khi ESD xảy ra có thể được xác định bằng cách giải phương trình vi phân cấp 2:

![]() với điều kiện đầu được cho bởi điện áp VESD: V(t=t0-) = VESD. Còn phương trình vi phân này từ đâu mà ra ư? Đơn giản chỉ là tổng điện áp trên một vòng kín thì bằng 0 thôi. Các số hạng trong vế bên trái lần lượt đại điện cho điện áp tức thời trên LESD, RESD, và CESD.

với điều kiện đầu được cho bởi điện áp VESD: V(t=t0-) = VESD. Còn phương trình vi phân này từ đâu mà ra ư? Đơn giản chỉ là tổng điện áp trên một vòng kín thì bằng 0 thôi. Các số hạng trong vế bên trái lần lượt đại điện cho điện áp tức thời trên LESD, RESD, và CESD.

Tôi từng thắc mắc tại sao trong phương trình nói trên không thấy sự hiện diện của điện áp Vcir(t) giữa hai I/O của “Mạch chịu tác động của ESD”. Thực ra nếu viết đầy đủ thì Vcir(t) sẽ xuất hiện trong một số hạng mới của vế bên trái. Tuy nhiên, nếu trong mạch có các thành phần bảo vệ ESD thì Vcir(t) sẽ rất nhỏ so với VESD. Chẳng hạn như trong mạch CMOS thì giá trị cực đại của Vcir(t) vào khoảng 2-3 Volt. Vì Vcir(t) không đáng kể so với các điện áp trên LESD, RESD, và CESD, nên nó thường được bỏ đi để giúp cho việc khảo sát dòng điện iESD(t) được đơn giản hơn. Tuy nhiên Vcir(t) vẫn rất đáng kể trong tương quan so sánh với điện áp hoạt động an toàn của “Mạch chịu tác động của ESD”. Ta sẽ thấy điều này trong các phần sau.

Với phương trình vi phân cấp 2 cùng với điều kiện đầu nói trên, tôi có thể tìm ra iESD(t) cho từng mô hình ESD. Tuy vậy, sự trợ giúp của Internet và một vài quyển sách toán về giải phương trình vi phân có lẽ vẫn chưa đủ đối với tôi. May mắn là vẫn có cách khác để tìm ra iESD(t): dùng một phần mềm mô phỏng mạch điện. Tất nhiên là có thể có những cách khác như dùng MATLAB nhưng tôi chưa thử. Do tôi có sẵn phần mềm Spectre nên tôi dùng Spectre. Tuy nhiên, với một mô phỏng đơn giản như thế này, bất cứ phiên bản miễn phí nào của SPICE cũng hoàn toàn có thể dùng được.

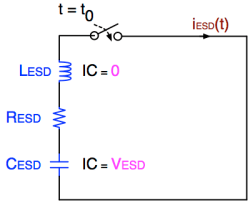

Hình 2: Sơ đồ mạch và các thiết lập về điều kiện đầu (IC = initial condition) trong mô phỏng dòng điện ESD dùng phần mềm mô phỏng mạch.

Khi dùng SPICE/Spectre mô phỏng dòng điện ESD, vì Vcir(t) được bỏ qua nên trong mô phỏng này không cần sơ đồ mạch của “Mạch chịu tác động của ESD” mà chỉ có một mạch RLC nối tiếp với các điều kiện đầu (initial condition) cho C và L như được trình bày trong Hình 2. Với Spectre, tôi còn phải mô phỏng thời điểm ESD bắt đầu bằng cách đặt một switch (công tắc) nối tiếp với mạch RLC và chỉ “đóng” cái switch này vào thời điểm t0. Nếu không có cái switch này trong mạch thì kết quả mô phỏng của tôi không giống với kết quả trình bày trong các tài liệu về ESD.

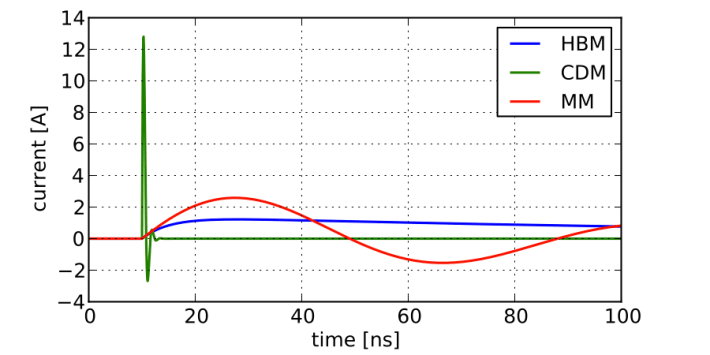

Hình 3 dưới đây trình bày kết quả mô phỏng các mô hình ESD trong Hình 2 với các thông số ESD trong Bảng 1 (xem Phần 2). Giá trị của dòng điện ESD, iESD(t), trong 3 mô hình ESD được vẽ theo thời gian. Quá trình phóng điện bắt đầu sau 10ns kể từ khi bắt đầu mô phỏng. Nghĩa là cái switch mà tôi đề cập bên trên sẽ ở trạng thái mở – không dẫn điện – trong vòng 10ns đầu tiên, rồi được chuyển sang trạng thái đóng – dẫn điện – kể từ thời điểm 10ns trở đi.

Dưới đây là một vài nhận xét về dòng điện ESD trong các kiểu phóng điện mà ta có thể rút ra từ kết quả mô phỏng:

- Mô hình HBM được mô phỏng với giá trị VESD lớn nhất (2kV) nhưng giá trị cực đại của iESD(t) lại thấp nhất, vào khoảng 1.3A. Lý do là vì RESD lớn (1.5kOhm). Vì vậy mặc dù yêu cầu về giá trị tối thiểu của VESD cho HBM thường khá cao (trong tầm vài kV), HBM chưa hẳn là mô hình khó “đỡ” nhất.

- Dòng điện ESD trong mô hình HBM có đáp ứng “chậm” nhất: thời gian lên (rise time) và xuống (fall time) đều dài. Lý do là vì LESD lớn (nhớ rằng cuộn cảm chống lại sự thay đổi nhanh của dòng điện). Thời gian lên có thể dài đến 6-8ns. Tổng thời gian phóng điện trong mô hình HBM là dài nhất và vào khoảng 300ns. Lý do là vì lượng điện tích nhiều hơn (do QESD = CESDxVESD) mà dòng điện cực đại (một cách nói khác của tốc độ xả điện tích) lại thấp hơn. Vậy nên các mạch bảo vệ HBM không cần phải có đáp ứng nhanh như các mạch CDM và MM.

- Năng lượng tổng cộng được giải phóng bởi dòng điện ESD trong mô hình HBM là cao nhất (theo công thức E = 0.5xCESDxVESD2). Bởi vì năng lượng này được giải phóng dưới dạng nhiệt nên phóng điện kiểu HBM có thể sẽ tạo stress nhiệt lớn nhất.

- Dòng điện ESD trong mô hình HBM chỉ chạy theo một hướng trong toàn bộ thời gian phóng điện. Việc dòng điện dù không cao nhưng chỉ chạy theo một hướng trong thời gian dài làm cho kiểu phóng điện HBM có thể gây ra hiệu ứng electromigration mạnh làm suy yếu các kết nối (interconnect) trong mạch. (Với cùng công suất, dòng điện xoay chiều không gây ra nhiều tác hại về electromigration như dòng điện một chiều. Hiểu một cách nôm na, dòng điện xoay chiều chỉ đá qua đá lại, vì nó xoay chiều mà, các phân tử vật chất cấu thành dây dẫn còn dòng điện một chiều thì đẩy hẳn các phân tử này về một đầu dây làm cho đầu dây bên kia bị đứt.)

- Sự phóng điện theo mô hình CDM tạo ra dòng điện có biên độ cao nhất trong thời gian ngắn nhất do RESD và LESD đều nhỏ. Bảo vệ mạch bán dẫn dưới tác động của ESD theo mô hình CDM có thể xem là khó khăn nhất vì mạch bảo vệ phải đáp ứng nhanh và phải dẫn được dòng điện lớn.

- Đặc tính về độ lớn và thời gian (rise time, fall time) của dòng điện ESD trong mô hình MM nằm ở mức trung gian so với các đặc tính tương ứng của dòng điện trong mô hình HBM và CDM. Bảo vệ ESD theo mô hình MM cũng có thể xem như có độ khó ở mức trung gian. Trong nhiều trường hợp, mạch bảo vệ ESD theo mô hình MM và HBM tương tự nhau còn mô hình CDM sử dụng một dạng mạch bảo vệ khác.

…