…

Khả năng chịu đựng dòng điện ESD của một con chíp có thể được nâng cao bằng cách bổ sung các mạch điện bảo vệ vào bên trong nó. Những mạch điện này phải được thiết kế để:

- Đáp ứng tốt với các đặc tính của dòng điện ESD, là xung điện có thời gian rất ngắn nhưng biên độ rất lớn, như đã tóm tắt ở cuối Phần 4.

- Trong điều kiện bình thường, nghĩa là khi không có ESD, chúng không tác động hoặc tác động không đáng kể đến tính năng và hiệu năng của mạch điện được bảo vệ.

Một con chíp bán dẫn sẽ tương tác về mặt điện với môi trường xung quanh thông qua các I/O hay “pin” (chân) của con chíp. Hiện tượng ESD cũng sẽ tác động lên chíp thông qua các I/O này. Cụ thể là dòng điện ESD sẽ chạy vào ở một I/O và chạy ra ở một I/O khác. Để đảm bảo dòng điện ESD không chạy qua các thành phần mạch khác ngoại trừ các mạch bảo vệ ESD, theo logic thông thường, ta phải đặt các mạch bảo vệ này ngay tại các I/O. Nói cách khác, khi vẽ layout cho chíp ta sẽ vẽ các mạch bảo vệ nằm ngay bên dưới hoặc nằm sát, tuỳ theo quy tắc thiết kế của công ty bán dẫn (foundry), với các I/O pad. Việc bảo vệ ESD cho con chíp chính là bảo vệ các I/O.

Hãy bàn sơ về các I/O trước khi nói về các mạch bảo vệ bởi vì với các loại I/O khác nhau ta sẽ có những cách bảo vệ khác nhau. Thực ra thì cũng chỉ có 2 loại I/O mà thôi:

- Loại thứ nhất là các I/O để cấp nguồn (power supply) cho chíp. Có thể là VDD, VSS, GND, DVDD, DVSS, AVDD, AVSS, AGND, vân vân và vân vân. Nói chung là các I/O không thuộc loại … thứ hai.

- Còn loại thứ hai là các I/O để đưa tín hiệu (signal) vào và ra khỏi chíp. Có thể là CLK, INPUT, OUTPUT, IREF, VREF, RESET, ENABLE, vân vân và vân vân. Nói chung là các I/O không thuộc loại … thứ nhất.

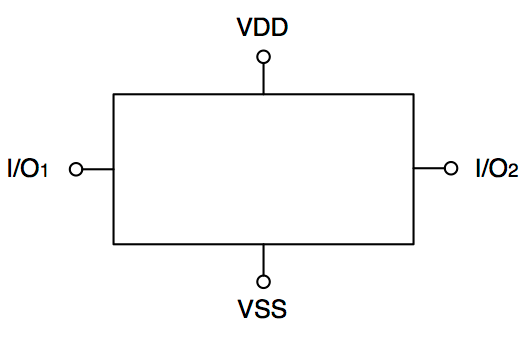

Thiết kế mạch bảo vệ các I/O cấp nguồn nhìn chung là ít “hại não” hơn là thiết kế mạch bảo vệ các I/O tín hiệu bởi vì ta không phải lo lắng về việc đảm bảo tín hiệu truyền qua không bị ảnh hưởng bởi các mạch bảo vệ ESD. Từ đây trở đi ta sẽ gọi các I/O cấp nguồn là VDD và VSS còn các I/O tín hiệu sẽ được gọi đơn giản là I/O. Ta sẽ xem xét việc bảo vệ ESD cho một con chíp đơn giản có một chân VDD, một chân VSS, và hai chân I/O như trong Hình 5.

Với con chíp đơn giản trong Hình 5 sẽ có các tình huống ESD sau đây xảy ra:

- Dòng điện ESD chạy vào (ra) ở VDD và chạy ra (vào) ở VSS

- Dòng điện ESD chạy vào (ra) ở một I/O và chạy ra (vào) ở VDD

- Dòng điện ESD chạy vào (ra) ở một I/O và chạy ra (vào) ở VSS

- Dòng điện ESD chạy vào ở một I/O và chạy ra ở một I/O khác

Thực ra với các con chíp chỉ sử dụng một nguồn cấp điện (single power domain) như trên, bất kể con chíp có bao nhiêu I/O, thì khi hiện tượng ESD xảy ra, dòng điện sẽ chỉ chạy theo một trong các tình huống ESD vừa liệt kê ở trên. Nếu con chíp sử dụng nhiều nguồn cấp điện (multiple power domain) ví dụ như con chíp có AVDD/AVSS cho mạch analog và DVDD/DVSS cho mạch digital thì sẽ có các tình huống ESD khác. Bây giờ ta chỉ xem xét mạch có một nguồn cấp điện và sẽ bàn về mạch có nhiều nguồn cấp điện sau này.

Bảo vệ ESD cho mạch sử dụng một nguồn cấp điện

Như đã được giới thiệu bên trên, ta sẽ bảo vệ con chíp bằng cách thêm các mạch ESD để tạo các đường dẫn dòng ESD giữa các chân của con chíp. Hình 6 mô tả cách kết nối các mạch ESD để bảo vệ cho một con chíp có một nguồn cấp điện. Các thành phần của mạch bảo vệ ESD, được minh hoạ bằng màu xanh, gồm có:

- Mạch ESD nối giữa VDD và VSS. Trên Hình 6, mạch này được minh hoạ bằng khối có nền màu xanh.

- Mạch ESD nối giữa các I/O và VDD hoặc VSS. Trên Hình 6, các mạch này được minh hoạ bằng khối có nền màu trắng.

- Các dây dẫn nối từ I/O, VDD, VSS đến các mạch ESD.

Trong 3 thành phần kể trên, dễ hiểu nhất có lẽ là các dây dẫn. Đơn giản chỉ là các dây kim loại được thiết kế sao cho có điện trở thấp: khi vẽ layout, các dây này phải rộng và nên kết hợp nhiều lớp kim loại với nhau. Có lẽ lý do duy nhất mà ta không vẽ các dây nối với các I/O rộng hết cỡ là việc điện dung ký sinh của các dây này có thể làm giảm băng thông của I/O. Các dây nối với VDD hay VSS thì ta có thể vẽ rộng thoải mái bởi vì điện dung ký sinh trên VDD và VSS giúp ổn định hoạt động của mạch.

…

(Phần 6: Bảo vệ ESD cho VDD và VSS với mạch “power clamp”)