SAN FRANCISCO, California và NUREMBERG, Đức — Freescale, Cisco và Ciena đã gạt bỏ những hoài nghi về công nghệ FD-SOI (fully-depleted silicon-on-insulator) bằng cách tiết lộ kinh nghiệm của họ về công nghệ này, với hy vọng là các công ty khác sẽ làm theo.

Tuần trước [24-26/2/2015 – người dịch], trong hội nghị Thế giới Công nghệ Nhúng (Embedded World conference) ở Nuremberg, Đức, công ty bán dẫn Freescale đã xác nhận họ đang thiết kế các chíp sử dụng công nghệ FD-SOI.

Geoff Lees, phó chủ tịch cấp cao đồng thời là tổng giám đốc chịu trách nhiệm về vi điều khiển ở Freescale đã nới với EE Times rằng công ty có kế hoạch sử dụng công nghệ 28nm FD-SOI cho thế hệ bộ vi xử lý kế tiếp của mình, i.MX 7.

Thứ Sáu vừa rồi (27/2), một kỹ sư trưởng làm việc cho Cisco Systems còn trình bày kinh nghiệm của Cisco về công nghệ FD-SOI trong một buổi thảo luận ở hội thảo về FD-SOI ở San Francisco.

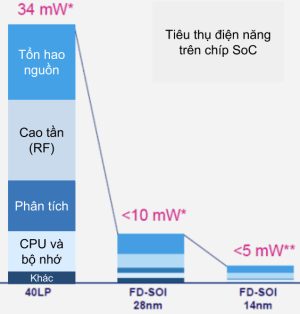

Guntram Wolski, kỹ sư trưởng quản lý thực hiện và thiết kế vật lý ở Cisco đã nói ở buổi thảo luận đó rằng ông thấy được những lợi ích của FD-SOI. Do dòng rò trong công nghệ này nhỏ hơn 4 lần so với công nghệ bulk, nên nó cho phép ta sử dụng các hệ thống làm mát đơn giản hơn và phù hợp với nhiều kiểu thiết kế hình dáng cho thiết bị.

Tương tự như vậy, Ciena cũng công khai tại hội thảo ở San Francisco rằng mình đang sử dụng FD-SOI.

Freescale, Cisco và Ciena đã tham gia hội sử dụng FD-SOI, cùng với tập đoàn Sony vốn trong tháng một đã tiết lộ rằng thế hệ tiếp theo của chíp GNSS (Global Navigation Satellite System – hệ thống vệ tinh giám sát toàn cầu) của mình sẽ sử dụng công nghệ 28nm FD-SOI.

STMicroelectronics, công ty phát triển công nghệ FD-SOI, đã hy vọng Globalfoundries cũng sẽ nhân dịp này thông báo rằng họ hỗ trợ công nghệ FD-SOI, nhưng vào phút cuối, hãng chế tạo chíp đã quyết định không phát biểu tại sự kiện ở San Francisco. Thay vào đó, một đại diện của Samsung đã công bố các kế hoạch cho dịch vụ dùng chung wafer (multi-project wafers – MPW) trên công nghệ FD-SOI, là dịch vụ mà STMicroelectronics đã cung cấp trong một thời gian.

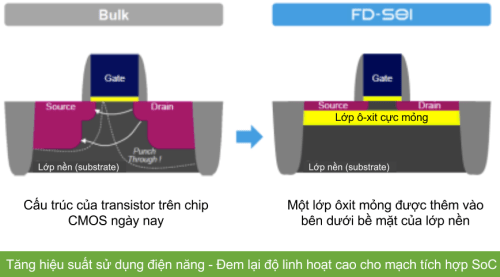

FD-SOI có lợi thế rất lớn về mặt tiêu thụ điện năng so với công nghệ bulk 28nm CMOS, nhưng công nghệ này cần thêm nhiều công cụ hỗ trợ, theo những người phát biểu của Cisco và Ciena. Cả hai công ty đều có vẻ như đã lên kế hoạch cho ra mắt các chíp tiếp theo sử dụng công nghệ này.

Freescale dùng FD-SOI cho IoT

Freescale đã công bố ở hội nghị Thế giới Công nghệ Nhúng một số dòng vi xử lý mới, trong đó có i.MX 6 SoloX. i.MX 6 là dòng vi xử lý ứng dụng có nhiều lõi không giống nhau, với tính năng bảo mật cấp thiết bị được xem là sẽ “đảm bảo an toàn” cho các ứng dụng IoT, bao gồm cả ô-tô (truyền tin, xe đến xe (vehicle-to-vehicle – V2V), và thông tin giải trí tối thiểu) và thiết bị thông minh (chăm sóc sức khỏe, phụ tùng nhà cửa và nhà máy tự động).

Trong khi vi điều khiển i.MX 6 được xây dựng trên công nghệ 40nm, thế hệ tiếp theo i.MX 7 sẽ được thực hiện trên công nghệ 28nm FD-SOI, theo lời của Geoff Lees (Freescale).

Khi được hỏi tại sao Freescale lại chọn FD-SOI, Lees đã nói với chúng tôi rằng với mức độ tích hợp mạch tương tự (analog) có khi lên đến 40% của Freescale thì công nghệ FIN-FET được dùng cho thiết kế số mật độ cao “sẽ không phù hợp”.

Freescale đã dùng FD-SOI trong thiết kế sơ bộ, nhưng để thực sự sử dụng công nghệ này thì họ phải chờ Samsung đánh giá chất lượng sản phẩm của quy trình chế tạo của chính Samsung. Freescale hy vọng sẽ không phải chờ lâu, có lẽ chậm nhất là tháng Năm, 2015.

Cisco, Ciena cũng dùng FD-SOI

Tại buổi thảo luận, khi được hỏi về số lượng chíp FD-SOI mà Cisco đang phát triển, Wolski đã xác nhận là có một chíp, nhưng ông cũng cho rằng có nhiều chíp nữa đang được chế tạo.

Thời điểm tham gia thị trường là câu hỏi thường tái diễn khi tranh luận về FD-SOI trong lĩnh vực bán dẫn, đặc biệt là khi một số công ty đã tiến hành thiết kế chíp sử dụng 14nm FinFET. Liệu các công ty có quay qua sử dụng FD-SOI hay không?

Wolski ở Cisco, là công ty đã làm việc với nhiều hãng chế tạo chíp và chắc không gắn bó cố định với một công nghệ nào, cho rằng công nghệ FD-SOI 28nm chẳng hạn, sẽ được dùng để sản xuất ra các chip có tiêu hao điện năng thấp với số lượng lớn.

Phát biểu về trải nghiệm của Cisco đối với FD-SOI, Wolski cho rằng công ty đã không thể sử dụng phân cực thân thuận (forward body biasing) trong công nghệ do thiếu sự hỗ trợ của công cụ mô phỏng. Tuy nhiên, ông hy vọng các công cụ này sẽ được dùng cho chíp tiếp theo.

Với chíp hiện tại, Wolski nói, “Tôi thấy công suất rò trên 28nm FD-SOI chỉ ở mức một nửa cho đến một phần tư [so sánh với công nghệ bulk], còn điện áp thì có thể thay đổi rất nhiều”. Ông nhấn mạnh rằng chíp có khả năng hoạt động mà không cần bộ tản nhiệt trong hệ thống tự động hóa công nghiệp.

“Mức tiêu hao điện năng thấp đến nỗi chúng tôi đã thôi không cần thiết kế một chíp khác mà đưa các tính năng của nó vào trong con chíp ASIC này – điều đó rất đáng kể khi nhìn từ khía cạnh kinh tế” Wolski còn nói thêm.

Tương tự, Ciena cũng đang sử dụng FD-SOI. “FD-SOI có lợi thế về công suất, hiệu năng của mạch tương tự (analog) và quan trọng nhất là giảm chi phí”, lời của Naim Ben-Hamida, quản lý thiết kế mạch tương tự tốc độ cao ở Ciena, khi mô tả bộ thu phát quang học tích hợp có tốc độ 100Gbit/s được chế tạo trên công nghệ này.

Hiệu năng của transistor trên FD-SOI tốt hơn 30% so với công nghệ bulk. Công nghệ này sử dụng ít lớp mặt nạ hơn, có tỉ lệ chíp được sản xuất thành công (yield) cao hơn và số lớp kim loại thì tương tự như bulk, Ben-Hamida nói. “Nói tóm lại, FD-SOI cho chúng ta thêm một cực cổng để điều chỉnh hiệu năng, kiểm soát transistor NMOS và PMOS… nhưng hiện tại các công cụ thiết kế còn chưa theo kịp, có lẽ điểm mấu chốt là khả năng của các công cụ hỗ trợ thiết kế,” ông nói thêm.

Chíp thu phát quang học về cơ bản tập hợp chức năng của các chíp 32nm và 65nm trước đó và một FPGA “vào trong một chíp mà chỉ tiêu hao một phần ba công suất so với cả ba chíp gộp lại”, ông nói thêm.

Đại diện của cả Cadence và Synopsys đều có mặt và trình bày chi tiết về khả năng hỗ trợ FD-SOI về mặt công cụ thiết kế và các khối sở hữu trí tuệ (IP).

STMicroelectronics hy vọng sẽ đưa phiên bản 14nm của công nghệ này vào sản xuất đại trà trong năm nay. Mặc dù được tối ưu về chi phí chế tạo nhưng mật độ của công nghệ này hiện chưa thể bằng với công nghệ 16/14nm FinFET.

Hiện chưa rõ liệu các kỹ sư có thể tìm ra chỗ đứng cho công nghệ FD-SOI ở mức 12 hay 10nm không, mặc dù các kỹ sư đang nghiên cứu, theo lời của Giorgio Cesana, giám đốc tiếp thị của ST và đồng giám đốc của Hiệp hội SOI. Phiên bản 7nm khó có thể thành hiện thực, ông nói thêm.

Quy trình 28nm dường như là điểm lý tưởng cho công nghệ FD-SOI. STMicroelectronics hy vọng có thể thu hút một số lượng lớn thiết kế cho ứng dụng IoT và các ứng dụng khác trên quy trình chế tạo này. Tại sự kiện ở San Francisco và sự kiện tương tự ở Tokyo đầu năm nay, ST luôn nhấn mạnh về FD-SOI cho ứng dụng hạ tầng mạng và tự động.

Theo ST, những ví dụ cụ thể về khả năng FD-SOI có thể cải thiện các chíp trong hạ tầng mạng bao gồm khả năng hoạt động tốt hơn, hiệu suất năng lượng tốt hơn, và khả năng thay đổi mức tiêu thụ năng lượng tùy theo yêu cầu hoạt động. Ngoài ra, tỉ lệ lỗi mềm thấp cho phép thiết kế bộ nhớ truy suất nội dung bậc ba (ternary content-addressable memory – TCAM) đơn giản hơn. TCAM là một loại bộ nhớ tốc độ cao đặc biệt có khả năng tìm kiếm trong toàn bộ nội dung của nó chỉ trong một xung nhịp.

Sức hút của công nghệ 28nm FD-SOI đang tăng lên, theo lời của hai chuyên gia công nghiệp giấu tên quen thuộc với công nghệ này. Tuy nhiên, công nghệ FinFET sẽ là xu hướng chủ đạo trong tương lai do có hiệu năng vượt trội, còn FD-SOI thì lại thiếu lộ trình xuống 7nm hoặc thấp hơn.

- Nguyên bản tiếng Anh: “Freescale, Cisco, Ciena Give Nod to FD-SOI” Junko Yoshida, EETimes, 1 Mar. 2015.

- Người dịch: Hồ Quang Tây

- Biên tập: Tạ Minh Chiến