Phần 2 và cũng là phần cuối của bài viết “3D Chips Grow Up” của Rachel Courtland đăng trên tạp chí IEEE Spectrum số tháng 1/2012 . (Xem Phần 1: FinFET.)

…

Công nghệ FinFET của Intel không phải là cách duy nhất để thoát khỏi giới hạn phẳng của con chíp. Trong năm 2012 sẽ có nhiều bước tiến trong một công nghệ khác còn triển vọng hơn: chồng các con chíp lên nhau và sử dụng các kết nối theo chiều thẳng đứng, giống như các ống thang máy trong các toà nhà chọc trời, để liên kết các con chíp lại. Nếu tất cả hoạt động trơn tru, công nghệ kết nối này sẽ đem lại những thiết bị nhanh hơn và hiệu quả hơn rất nhiều, cho dù chúng có sử dụng các transistor theo công nghệ cũ.

Ở một vài khía cạnh, 3-D không phải là điều gì mới đối với các nhà sản xuất chíp. Các chíp nhớ flash đã được xếp chồng lên với nhau để giảm thể tích và tăng tốc độ. Tuy nhiên việc xếp chồng các chíp lên nhau vẫn bị giới hạn bởi khả năng kết nối chúng lại với nhau. Hiện tại các kết nối này không đi xuyên qua con chíp silicon mà phải đi vòng qua chúng với khoảng cách hàng milimét do đó làm suy yếu và biến dạng các tín hiệu tốc độ cao truyền qua chúng. Đã thế, lại không có nhiều khoảng trống để tạo các kết nối theo phương nằm ngang. Những đường nối hẹp nhất cũng rộng cỡ 25 micromét và chúng phải nằm theo các cạnh của con chíp vậy nên số lượng kết nối cho mỗi con chíp sẽ bị hạn chế.

(Nguồn: MANA)

Vì những lý do đó, việc tạo ra được những kết nối theo phương thẳng đứng xuyên qua các con chíp sẽ trở nên rất hữu ích. Nếu các nhà làm chíp có thể sản xuất các kết nối này (thường được gọi là TSV – through silicon via) với giá hợp lý, họ có thể có nhiều kết nối hơn bằng cách làm cho chúng nhỏ lại. Đi xuyên qua con chíp thay vì đi vòng qua các cạnh còn giúp giảm chiều dài của các kết nối từ vài millimét xuống còn 50 micromét hay thậm chí ngắn hơn tuỳ thuộc vào độ dày của con chíp. Công nghệ này rất có tiềm năng. Samsung, một trong những công ty đang nghiên cứu cách dùng TSV để kết nối các chíp nhớ DRAM, ước lượng rằng việc dùng các kết nối thẳng đứng sẽ giảm một nữa năng lượng tiêu hao, tăng băng thông lên 8 lần, và giảm kích thước khoảng 35%. “Lợi ích mà công nghệ này đem lại thật là phi thường,” Sitaram Arkalgud, người quản lý chương trình nghiên cứu kết nối 3-D ở Sematech, nói. “Những cải tiến mang tính cách mạng như thế này không xảy ra thường xuyên đâu.”

Để làm các kết nối TSV, nhà sản xuất phải tạo ra những lỗ sâu và hẹp xuyên qua tấm nền silicon. Tiếp theo đó họ phủ một lớp chất cách điện lên mặt trong của những lỗ này. Cuối cùng các lỗ được lấp đầy bởi đồng. Vấn đề là khi tấm silicon nóng lên, đồng giãn nở gấp 5 lần silicon nên có thể làm hỏng tấm silicon.

Việc bảo quản những tấm silicon trong quá trình sản xuất cũng là một khó khăn. Mỗi tấm silicon phải được làm mỏng xuống còn khoảng 50-micromét nghĩa là còn mỏng hơn cả một sợi tóc người. Những tấm nền mỏng như vậy có thể bị uốn cong như những lớp vỏ gỗ được tạo ra khi ta gọt bút chì. Các nhà làm chíp phải gắn những tấm nền silicon lên các đĩa một cách tạm thời để giữ chúng ổn định trong quá trình xử lý.

Tuy nhiên các nhà quan sát nói rằng hầu hết các trở ngại kỹ thuật đã được giải quyết. Trong năm nay, các công ty sẽ tìm cách làm TSV mà không làm tăng đáng kể chi phí sản xuất chíp. Đây là “năm mà chúng tôi phải tìm ra cách sản xuất chúng đại trà. Phải phát triển quy trình sản xuất và tăng xác suất thành công,” E. Jan Vardaman, chủ tịch của TechSearch International (Austin, Texas) nói.

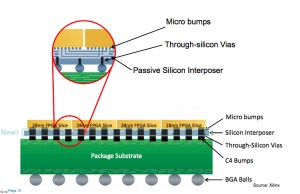

Trong thực tế, bước phát triển đáng kể nhất trong năm tới có thể chỉ là tạo ra được những kết cấu xếp tầng (stack) đơn giản thường được gọi là 2.5D. Trong phương pháp này các TSV được chạy xuyên qua một lớp silicon trung gian, được gọi là “interposer”, nằm giữa con chíp và bảng mạch điện tử. Có lẽ công nghệ này chỉ là công nghệ 2-D. Tất cả các con chíp (đã được đóng gói) cần thiết cho một thiết bị, ví dụ như bộ thu sóng cao tần, bộ xử lý đồ hoạ, bộ nhớ, mạch logic, trước tiên được đặt trên mặt của bo mạch chủ. Sau đó, thay vì dùng các đường dây đồng chạy trên bo mạch chủ để nối các con chíp lại với nhau, người ta dùng các TSV chạy xuyên qua lớp interposer có các lớp dây dẫn nằm theo phương ngang để tạo ra kết nối. Bằng cách đưa tất cả các kết nối ra khỏi bề mặt của bo mạch chủ, các con chíp có thể được đặt sát nhau để tiết kiệm diện tích và năng lượng.

Một trong những công ty tiên phong trong lĩnh vực interposer là Xilinx, công ty có trụ sở ở San Jose, California. Xilinx sử dụng TSV để kết nối bốn chíp FPGA đơn để tạo ra một chíp FPGA lớn nhất thế giới. Con chíp này chứa gần 7 tỷ transistor nghĩa là hơn 50% so với con chíp FPGA đơn lớn nhất, theo Xilinx. Xilinx ước tính rằng con chíp này tiêu thụ năng lượng ít hơn 1/5 so với năng lượng cần thiết cho một nhóm tương đương các FPGA đơn lẻ kết nối với nhau theo phương pháp thông thường.

Bên trong FPGA Virtex-7 200T của Xilinx – từ dưới lên: tấm nền của con chíp (packaging substrate), lớp interposer bằng silicon, và bốn chíp FPGA đơn. (Hình: Xilinx)

Công nghệ TSV cũng không đi sau công nghệ 2.5D là bao. Elpida, Micron, Samsung, và Toshiba đang trong quá trình xây dựng các chíp nhớ sử dụng TSV. Vài công ty đã chuyển các sản phẩm thử nghiệm đến cho khách hàng. Các nhà quan sát hy vọng rằng trong năm 2012, các bộ nhớ cao cấp, cho trong máy chủ và các máy tính hiệu suất cao, dùng công nghệ TSV sẽ ra đời. “Chúng ta sẽ thấy TSV bắt đầu được dùng trong các ứng dụng yêu cầu hiệu suất cao và không bị giới hạn về chi phí,” Jim Walker, phó chủ tịch nghiên cứu của Gartner chuyên theo dõi các phát triển về công nghệ đóng gói (packaging), nói. Các chíp nhớ là điểm khởi đầu hợp lý cho công nghệ 3D bởi vì chúng ít bị ảnh hưởng của sự co giãn nhiệt, Walker nói. Các nhà sản xuất, Walker cho biết, vẫn chưa tìm ra cách nào tốt để giải nhiệt cho các chíp khi chúng được xếp chồng lên nhau. Vấn đề còn trở nên gai góc hơn khi ta ghép nối các chíp khác loại với nhau. “Chíp đồ hoạ có thể nóng như một lò nướng,” Walker nói. “Nếu ta đặt các chíp nhớ hay chíp cao tần lên bên trên nó, ta sẽ có các bộ tạo nhiệt với suất giãn nở nhiệt khác nhau.” Kết quả là các con chíp sẽ không chạy tốt hoặc không bền.

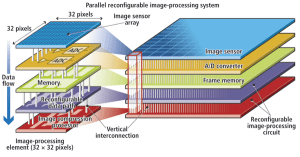

ZyCube dùng công nghệ TSV để xây dựng một bộ xử lý ảnh 3-D bao gồm một cảm biến ảnh, bộ chuyển đổi analog-digital, bộ nhớ, và một bộ xử lý có thể cấu hình lại được. (Nguồn: Vision-Systems.)

Còn có nhiều vấn đề lớn khác cần phải giải quyết khi các nhà sản xuất chế tạo những chíp phức tạp hơn. Làm sao để đảm bảo hai con chíp từ hai công ty khác nhau có thể kết nối được với nhau. Có cách nào ít tốn kém để kiểm tra khả năng hoạt động của từng con chíp đơn trong một con chíp lớn? Và nếu con chíp thành phẩm không hoạt động, làm sao xác định được nguyên nhân?

TSMC đã trải qua một thời gian khó khăn với câu hỏi cuối cùng khi họ cố gắng đưa công nghệ “interposer” vào sản xuất trong nữa sau năm 2012. “Khi chúng tôi bắt đầu phát triển TSV, chúng tôi làm theo cách truyền thống,” Doug Chen-Hua Yu, người đứng đầu bộ phận nghiên cứu và phát triển công nghệ kết nối (interconnect) và đóng gói (packaging) của TSMC, nói. Yu cho biết trước kia TSMC thường gửi các wafer thành phẩm sang cho các công ty chuyên đóng gói xử lý tiếp. Tuy nhiên, các wafer đã được làm mỏng sẽ rất dễ bị hư hỏng. Khi việc này xảy ra, “sẽ rất khó để quay lại xem thử ai đã làm gì sai,” Yu nói. “Đó có thể là nhà máy bán dẫn, hoặc là công ty đóng gói, hoặc là FedEx. Chúng tôi không thể biết được.”

Thậm chí ngay cả khi các wafer đã được kiểm tra kỹ lưỡng trước và sau khi vận chuyển, vẫn có những hư hỏng ngầm sẽ chỉ xuất hiện khi wafer đang được xử lý. Vì thế, Yu cho biết, hiện nay TSMC đang cố gắng xử lý hầu hết các công đoạn sản xuất wafer và đóng gói với công nghệ TSV ngay tại các cơ sở của TSMC.

Có một loạt các vấn đề về trách nhiệm liên đới, tiêu chuẩn công nghiệp, và quy trình sản xuất đang chờ được giải quyết. Tuy nhiên, dường như không ai cho rằng sẽ có những khó khăn không thể vượt qua trong công nghệ TSV. “TSV đang làm thay đổi cách thức chúng ta quản lý chuỗi cung ứng. Đó là lý do tại sao chúng ta mất nhiều thời gian để đưa công nghệ này vào sản xuất,” Arkalgud nói. “Nhưng một khi nó trở thành hiện thực, nó sẽ hữu ích khá lâu đấy.”

- Nguyên bản tiếng Anh: “3-D Chips Grow Up,” Rachel Courtland, IEEE Spectrum Magazine, January 2012.

- Người dịch: Tạ Minh Chiến

- Hiệu chỉnh: Phạm Duy Đông

- Bài viết có sử dụng hình ảnh và tư liệu bên ngoài để minh hoạ thêm cho nguyên bản tiếng Anh